© 2023 Digital Dynamics, Inc. All rights reserved.

Interlock Builder<sup>™</sup>, The Industrial IOT Company<sup>™</sup>, Digital Dynamics<sup>™</sup> are the property of Digital Dynamics, Inc. Other products mentioned in this document are trademarks or registered trademarks of their respective holders.

Digital Dynamics, Inc | 5 Victor Square, Scotts Valley, CA 95066 Tel: 831-438-4444 | https://www.digitaldynamics.com

### Contents

| 1 | OVE   | RVIEW          |                            | 6  |

|---|-------|----------------|----------------------------|----|

|   | 1.1   | Interlock Buil | der                        | 6  |

|   | 1.2   | Fusion.IO Sys  | tem                        | 7  |

|   | 1.3   | Project Orgar  | nization                   | 7  |

|   | 1.4   | Features and   | Benefits                   | 8  |

| 2 | INST  | ALLATION       |                            | 9  |

|   | 2.1   | System Requi   | irements                   | 9  |

|   | 2.1.3 | 1 Operatir     | ng System Requirements     | 9  |

|   | 2.1.2 | 2 Hardwar      | re Requirements            | 9  |

|   | 2.2   | Downloading    | the Software               | 9  |

|   | 2.3   | Installing the | Software                   | 10 |

|   | 2.4   | Configuring th | he Static IP Address       | 12 |

|   | 2.5   | Starting Inter | lock Builder               | 13 |

|   | 2.6   | Adjusting the  | DPI Settings               | 13 |

|   | 2.7   | Creating an Ir | nterlock Builder project   | 14 |

| 3 | USE   | R INTERFACE T  | TOUR                       | 15 |

|   | 3.1   | Dockable Viev  | ws                         | 16 |

|   | 3.2   | Schematic Vie  | ew                         |    |

|   | 3.3   | System View    |                            | 19 |

|   | 3.4   | Interlocks Vie | ew                         | 19 |

|   | 3.5   | Monitor View   | /                          | 21 |

|   | 3.6   | Schematic Mo   | onitor View                | 23 |

|   | 3.6.2 | 1 Live Mor     | nitor Schematic Indicators | 23 |

|   | 3.7   | Field Connect  | t View                     | 24 |

|   | 3.8   | Properties Vie | ew                         | 25 |

|   | 3.8.2 | 1 Block Pro    | operties                   | 26 |

|   | 3.9   | Log Output V   | iew                        | 27 |

|   | 3.10  | Schematic Pro  | operties                   | 27 |

|   | 3.10  | ).1 Adding a   | and Importing Labels       | 27 |

|   | 3.10  | ).2 Import la  | abel default behavior      | 28 |

|   | 3.11  | Toolbars       |                            | 29 |

|   | 3.11  | 1 Standard     | d Toolbar                  | 29 |

|   | 3.11  | 2 Schemat      | tics Toolbar               | 29 |

|   | 3.11  | 3 Program      | n Toolbar                  | 29 |

|   |       | -              |                            |    |

|   |     | 3.11.4  | Monitor Toolbar                      | 29 |

|---|-----|---------|--------------------------------------|----|

| 4 |     | DESIGNI | NG INTERLOCKS                        | 30 |

|   | 4.1 | 1 Inte  | erlock Tutorial                      | 31 |

|   | 4.2 | 2 Sch   | ematic Blocks                        | 36 |

|   | 4.3 | 3 1/0   | Ports                                | 37 |

|   |     | 4.3.1   | Adding Labels to I/O Ports           | 38 |

|   | 4.4 | 4 Log   | ic Gates                             | 39 |

|   |     | 4.4.1   | Buffer                               | 39 |

|   |     | 4.4.2   | AND Gate                             | 39 |

|   |     | 4.4.3   | OR Gate                              | 39 |

|   |     | 4.4.4   | XOR Gate                             | 39 |

|   | 4.5 | 5 Tim   | ers                                  | 40 |

|   |     | 4.5.1   | Overview of Timer Functions          | 40 |

|   |     | 4.5.2   | Timer Period Properties              | 42 |

|   |     | 4.5.3   | Timer ON Details                     | 43 |

|   |     | 4.5.4   | Timer OFF Details                    | 44 |

|   |     | 4.5.5   | Timer PULSE Details                  | 45 |

|   |     | 4.5.6   | Embedded Timers                      | 45 |

|   | 4.6 | 6 Late  | ches                                 | 47 |

|   |     | 4.6.1   | Hardware Latch                       | 47 |

|   |     | 4.6.2   | Armed Latch                          | 48 |

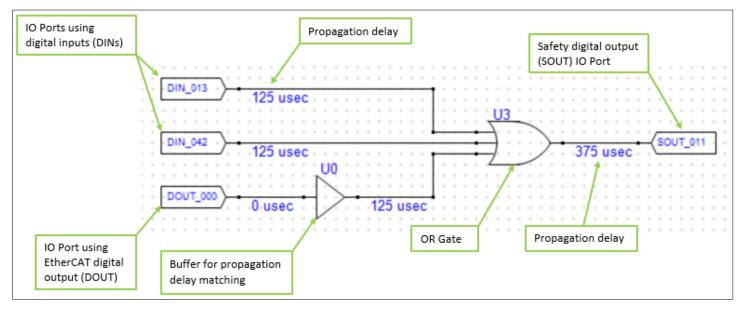

|   | 4.7 | 7 Inte  | erlock Propagation Delay             | 48 |

|   |     | 4.7.1   | Adding Delays with Buffers           | 49 |

|   |     | 4.7.2   | Matching Delays by Inverting Signals | 50 |

|   |     | 4.7.3   | Matching with Logic Design           | 50 |

| 5 |     | INTERLC | CK DESIGN TOOLS                      | 51 |

|   | 5.1 | 1 Pla   | cing Schematic Blocks                | 51 |

|   | 5.2 | 2 Sele  | ecting Objects                       | 52 |

|   |     | 5.2.1   | Selecting Single Objects             | 52 |

|   |     | 5.2.2   | Selecting Multiple Objects           | 52 |

|   |     | 5.2.3   | Adding and Deselecting with CTRL Key | 52 |

|   | 5.3 | 3 Mo    | ving Objects                         | 53 |

|   |     | 5.3.1   | Moving Single Objects                | 53 |

|   |     | 5.3.2   | Moving Multiple Objects              | 53 |

|   | 5.4 | 4 Inv   | erting Pins                          | 54 |

|   | 5.5 | 5 Wir   | ing Blocks                           | 55 |

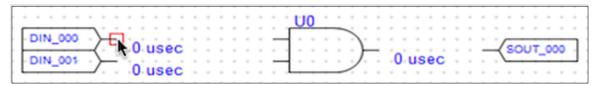

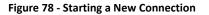

|   | 5.5.2 | 1 Example #1: Simple Connection Between Blocks | 55 |

|---|-------|------------------------------------------------|----|

|   | 5.5.2 | 2 Example #2: Drawing Multiple Wire Segments   | 56 |

|   | 5.5.3 | 3 Deleting Wire Segments                       | 57 |

| 6 | PRO   | GRAMMING INTERLOCKS                            | 58 |

|   | 6.1   | Configuring a safe analog card                 | 59 |

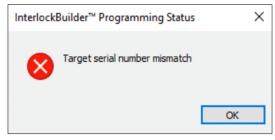

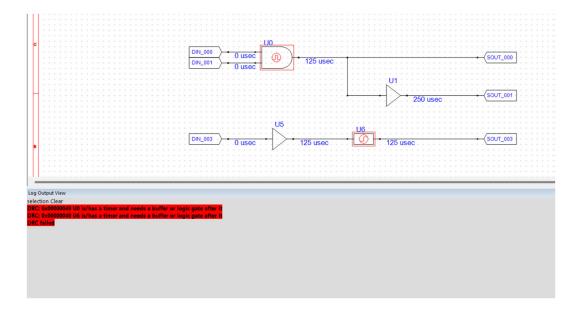

|   | 6.2   | Troubleshooting Programming Errors             | 60 |

| 7 | FILE  | AND PRINT FUNCTIONS                            | 63 |

|   | 7.1   | Saving and Opening Projects                    | 63 |

|   | 7.2   | Importing Files                                | 63 |

|   | 7.3   | Exporting Interlock Files                      | 63 |

|   | 7.4   | Printing Schematics                            |    |

| 8 | GLO   | SSARY                                          | 64 |

## **1 OVERVIEW**

### **1.1 INTERLOCK BUILDER**

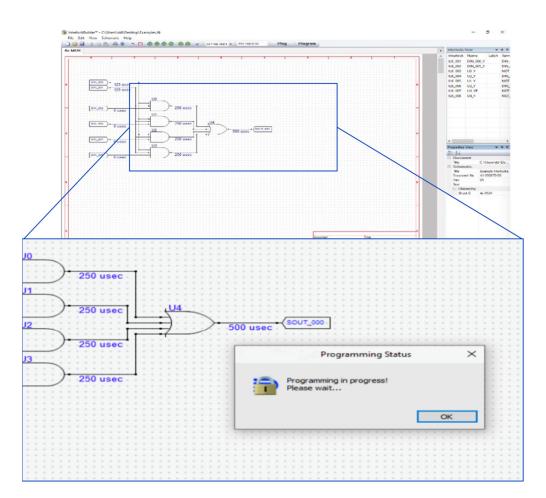

The Interlock Builder<sup>™</sup> application allows automation and machine system designers to implement software based, TÜVcertified safety interlocks for Fusion.IO systems. User defined interlocks control digital output states based on logic conditions which are applied to the state(s) of one or more digital inputs. Once designed, interlocks are programmed into a Fusion.IO system and their status can be monitored within Interlock Builder during testing.

Digital I/Os and logical conditions are available as blocks in Interlock Builder's schematic design environment which can be dropped into a schematic and wired together to create interlocks. Logical conditions which are available include:

- AND, OR, XOR gates

- Buffers

- Latches

Interlock Builder also provides protections to secure programmed interlocks and user data such as:

- AES 256-bit encryption and RSA 4096-bit authentication of schematic project files and exported interlocks

- Robustness for handling communication and power interruption between the PC and Fusion device

• Tamper prevention of existing interlocks in a Fusion.IO system

### **1.2 FUSION.IO SYSTEM**

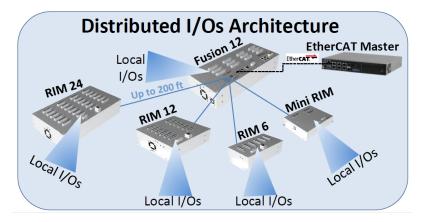

A Fusion.IO system is an I/O control platform which is comprised of one Fusion device and one or more Remote Interface Module (RIM) devices. Each Fusion or RIM device is configured with a selection of user defined slot cards which provide a high density of digital and analog I/O channels as well as other channel types such as serial (RS232 and RS485), temperature measurement (thermocouple and resistance temperature detectors (RTD)), and relay output. The safety implementation of a Fusion.IO system allows I/O channels from one or more of its connected devices to be used when designing safety interlocks. For example, I/O channels from the main Fusion and one or more RIM devices can be combined into safety rated interlocks.

**Figure 2-- Distributed Architecture**

### **1.3 PROJECT ORGANIZATION**

Interlock projects are saved as a single, encrypted file. Multiple schematic sheets can be created for projects, where each sheet is shown as a separate tab. Schematic sheets can be imported or exported. This helps you organize sections of interlocks by functional purpose, machine segments, etc. Project title, document number, revision, and names of individual schematic sheets can be assigned in the Properties View. Field Connects can be exported to unencrypted comma delimited (CSV) files. Schematics can be exported as schematic file or a bitmap.

### **1.4 FEATURES AND BENEFITS**

#### EASE OF CONFIGURATION

Safety interlocks are quickly and easily designed and programmed using Interlock Builder's schematic design environment, eliminating lengthy hardware design cycles.

#### DISTRIBUTED SAFETY INTERLOCKS

I/Os used in interlocks can span across distributed Fusion and Remote Interface Module (RIM) systems while still allowing system designers to achieve Safety Integration Level SIL 3 safety functions.

#### **INTRINSIC SECURITY**

Encryption and tamper protection features are built into the core of Interlock Builder to secure both project files and interlock programming of Fusion systems.

#### **ONLINE MONITORING**

Status of all I/O channels are monitored while Interlock Builder is connected online with a Fusion system, allowing debugging of interlocks as well as testing and troubleshooting during system commissioning.

## 2 INSTALLATION

This chapter provides the system requirements and the installation instructions.

### **2.1 SYSTEM REQUIREMENTS**

Your system needs to meet the following requirements to be able to install Interlock Builder.

#### 2.1.1 Operating System Requirements

The following operating systems are supported:

- Windows 10 (32 or 64 bit)

- Windows 11 (64 bit)

#### 2.1.2 Hardware Requirements

Interlock Builder requires the following:

- Interlock Builder requires 30MB of disk space

- Ethernet connection to the Fusion.IO system using a static IP address

- Static IP Address assign to PC network adapter which is compatible with the Fusion.IO system's IP address

A Fusion system's default IP is 192.168.9.50

#### 2.2 DOWNLOADING THE SOFTWARE

Please contact Digital Dynamics for instructions to download the current version of Interlock Builder.

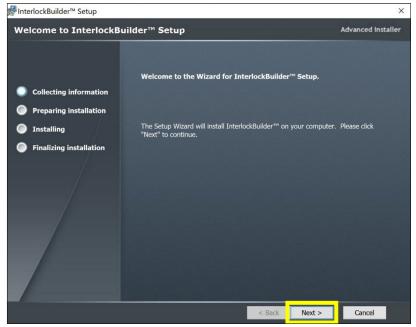

### 2.3 INSTALLING THE SOFTWARE

1. If an older version Interlock Builder is already installed, the existing version should first be uninstalled through the Windows Apps & Features settings:

| ← Settings             | - □ >                                                                                              | < |

|------------------------|----------------------------------------------------------------------------------------------------|---|

| Home                   | Apps & features                                                                                    |   |

|                        | 11VIEL CORP 4/20/2022                                                                              |   |

| Find a setting         | Intel® Management Engine Components 412 MB<br>9/17/2021                                            |   |

| IΞ Apps & features     | Intel® Optane™ Memory and Storage Management         16.0 KB           INTEL CORP         4/5/2022 |   |

| I⊐ Default apps        | Intel® Serial IO<br>9/17/2021                                                                      |   |

| 邱 <u></u> Offline maps | InterlockBuilder™         16.5 MB           4/4/2022                                               |   |

| Apps for websites      | 1.0.0                                                                                              |   |

| D Video playback       | Modify Uninstall                                                                                   |   |

|                        | Java 8 Update 66 88.9 MB 10/1/2021                                                                 |   |

Figure 4 - Uninstall through Windows Apps & Features

- 2. Navigate to the folder where the Interlock Builder installation file is located.

- 3. Double-click the installation file "InterlockBuilder\_vX.X.X.msi".

- 4. After the Interlock Builder Setup window appears, click Next.

Figure 5 - Interlock Builder Setup

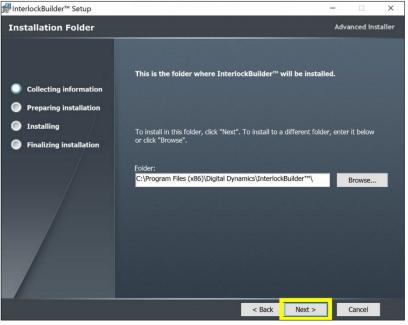

5. When the Installation Folder window appears, select the location where Interlock Builder should be installed, if you want to use a different location than the default. Click Next to continue.

Figure 6 - Installation Location

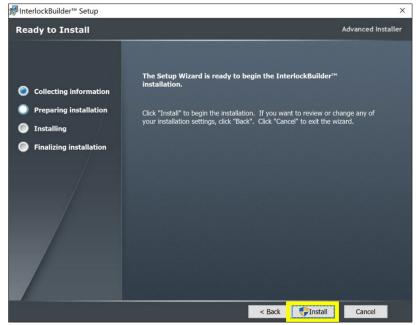

6. After the Ready to Install window appears, click Install to start the installation.

Figure 7 - Ready to Install

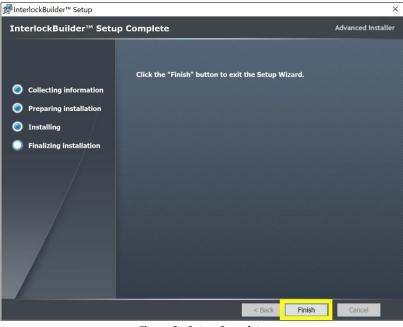

7. After the Interlock Builder Setup Complete window appears, click Finish to complete the installation process.

Figure 8 - Setup Complete

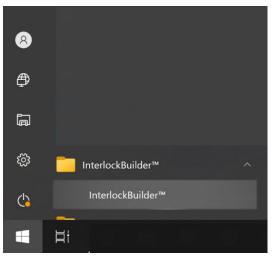

Interlock Builder is now available in from the Windows Start menu.

#### 2.4 CONFIGURING THE STATIC IP ADDRESS

If your network environment uses dynamic IP addresses, you can set up a second static ethernet connection to the Fusion.IO system.

To set up a second ethernet adaptor in Windows 11

- 1. Add a USB to Ethernet connector to the computer used to control the Fusion.IO system. Use this connector to connect to the Fusion.IO system using the provided cable. Verify that the Ethernet jack status lights up.

- 2. Click the Windows button then navigate to Settings > Network & Internet > and click Advanced Network Settings.

- 3. Select the USB to ethernet adaptor. (It may say Ethernet Adapter #2.)

- 4. Scroll down and click View Additional Properties.

- 5. Click Edit next to IP Assignment and choose Manual.

- 6. Assign a static IP Address to USB to PC network adapter that is a value lower than the Fusion system's default IP address of 192.168.9.50. For example, you can set it to 192.168.9.40.

#### 2.5 STARTING INTERLOCK BUILDER

To start using Interlock Builder, click the Interlock Builder Program in the Windows Start menu.

Figure 9 - Interlock Builder in Windows Start Menu

#### 2.6 ADJUSTING THE DPI SETTINGS

If you are using high DPI displays, you may see issues with how the Interlock Builder user interface appears. For example, the size and clarity of UI elements such as text, toolbars, application icons, application windows, dialog boxes, etc., may need to be adjusted. If needed, you can change the Windows DPI settings for Interlock Builder.

To adjust the DPI settings:

- 1) Close Interlock Builder.

- 2) Right-click the application and select Properties.

- 3) Select the Compatibility tab and click the "Change high DPI settings" button (Figure 10 Interlock Builder Application Properties).

- 4) Change the following High DPI scaling override settings (Figure 11 High DPI Settings):

- a. Select "Override high DPI scaling behavior".

- b. Set "Scaling Performed by" to "System".

- 5) Run Interlock Builder and confirm that your display symptoms have been resolved.

| , InterlockBuilder™ I                           | Properties             |           | ×                         |

|-------------------------------------------------|------------------------|-----------|---------------------------|

| Security<br>General                             | Details<br>Shortcut    |           | s Versions<br>npatibility |

| If this program isn't w<br>running the compatib |                        |           | /indows, try              |

| Run compatibility                               | troubleshooter         |           |                           |

| How do I choose con                             | npatibility settings n | nanually? |                           |

| Compatibility mode                              |                        |           |                           |

| Run this progra                                 | m in compatibility m   | ode for:  |                           |

| Windows 8                                       |                        | $\sim$    |                           |

| Settings                                        | node                   |           |                           |

| 8-bit (256) color                               | $\sim$                 |           |                           |

| Run in 640 x 48                                 | 0 screen resolution    |           |                           |

| Disable fullscree                               | en optimizations       |           |                           |

| Run this progra                                 | m as an administrat    | tor       |                           |

| Register this pro                               | ogram for restart      |           |                           |

| Change hig                                      | h DPI settings         |           |                           |

| Change settir                                   | ngs for all users      |           |                           |

|                                                 | ОК                     | Cancel    | Apply                     |

| InterlockBuilder™ Properties                                                                                                                                                                                                                           | × |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Choose the high DPI settings for this program.                                                                                                                                                                                                         |   |

| Program DPI                                                                                                                                                                                                                                            |   |

| Use this setting to fix scaling problems for this program<br>instead of the one in Settings<br>Open Advanced scaling settings                                                                                                                          |   |

| A program might look blurry if the DPI for your main display<br>changes after you sign in to Windows. Windows can try to fix<br>this scaling problem for this program by using the DPI that's<br>set for your main display when you open this program. |   |

| Use the DPI that's set for my main display when                                                                                                                                                                                                        |   |

| I signed in to Windows $\qquad \qquad \lor$                                                                                                                                                                                                            |   |

| Learn more                                                                                                                                                                                                                                             |   |

| High DPI scaling override                                                                                                                                                                                                                              |   |

| Override high DPI scaling behavior.<br>Scaling performed by:                                                                                                                                                                                           |   |

| System ~                                                                                                                                                                                                                                               |   |

| OK Cancel                                                                                                                                                                                                                                              |   |

|                                                                                                                                                                                                                                                        |   |

Figure 11 - High DPI Settings

Figure 10 - Interlock Builder Application Properties

### 2.7 CREATING AN INTERLOCK BUILDER PROJECT

You should have received a .ILK file that contains information about your hardware. You can use that file to create an Interlock Builder project.

That file supports a range of identical systems to be programmed with one system project file.

1. Open Interlock Builder.

Digital Dynamics

- 2. From the File menu, choose Open, and navigate to the ILK file.

- 3. Select it and click Open.

- 4. If you have schematics or field connect information that you want to use, from the File menu, choose Import.

- 5. To import schematic files, select Schematic, navigate to the .SCD file you want to use and click Open.

- 6. To import field connect data, select Field Connect, navigate to the .CSV file you want to use and click Open.

- 7. From the File menu, click Save As and name your new project file, then click Save.

- 8. Start drawing schematics, adding labels, and setting properties in your new file.

## **3 USER INTERFACE TOUR**

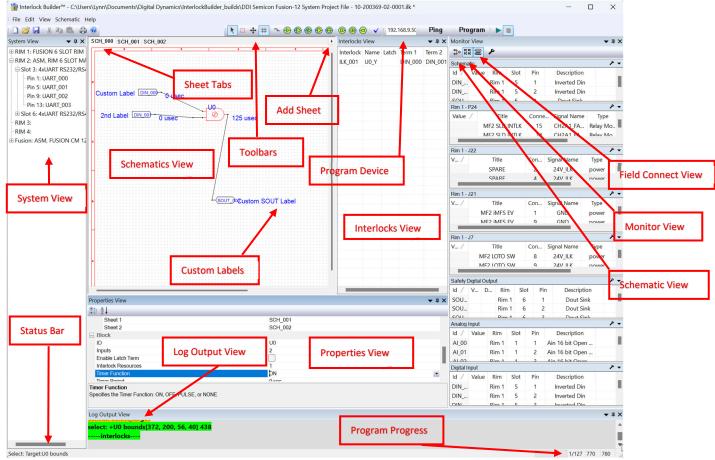

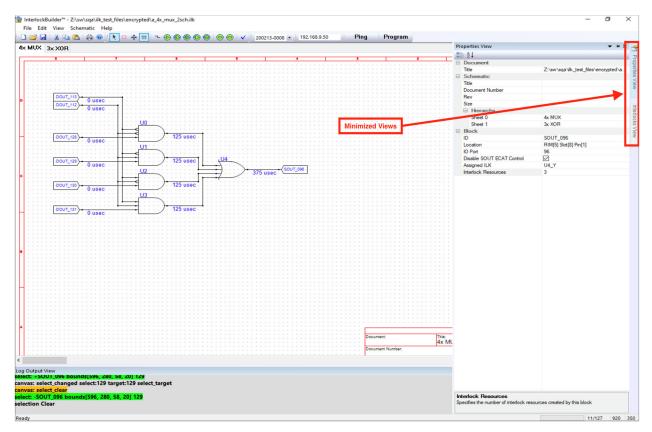

The main Interlock Builder application window contains:

- Schematics area where interlock logic can be designed using one or more tabbed schematic sheets

- Menu bar and toolbars which provide access to file management, schematic editing & programming, and view control functions

- Dockable panes, including individual views for Interlocks, Properties, Monitor (including Schematic and Field Connect), and Log Output views

Figure 12 - Main Interlock Builder Window

The Monitor View, Schematic View, and Field Connect View share the same pane. Click the icons to switch the view.

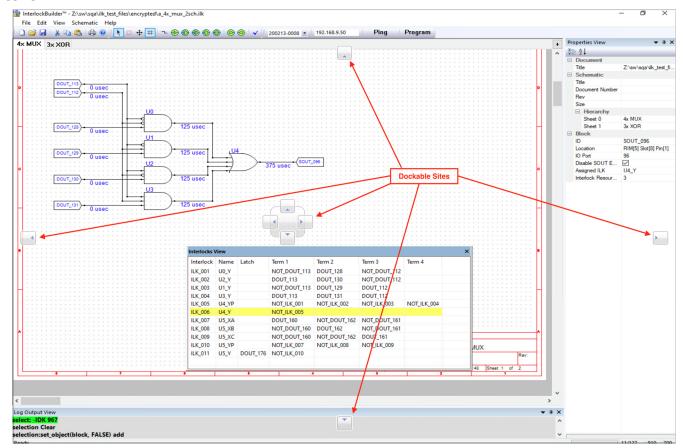

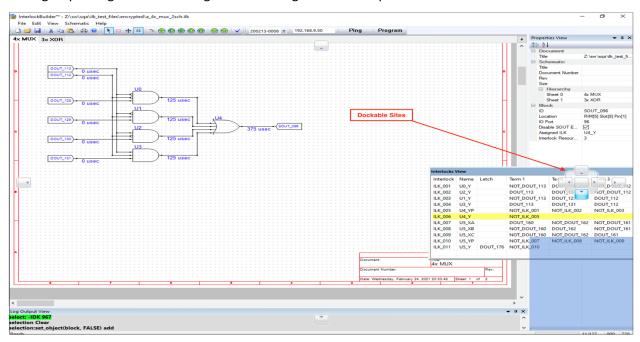

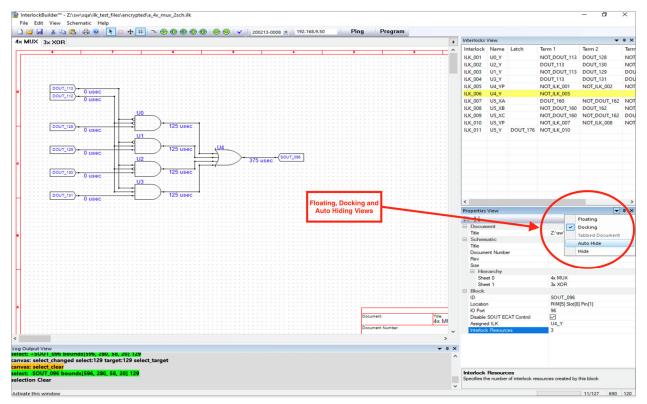

#### **3.1 DOCKABLE VIEWS**

The Interlocks View, Properties View, Monitor and Field Connect Views, and Log Output View are dockable panes which can be repositioned at the left, right, top, or bottom of the main window. They can also be set as floating windows or grouped together in a tabable pane. Use the View menu to open any panes not currrently open.

Dragging a view title bar shows the dockable sites where it can be relocated.

Figure 13 - Docking Sites

Panes can be grouped together in docking sites or arranged as tabbed panes.

Figure 14 - Docking Sites (grouped)

Click the arrow located in the title bar of any pane to show options to Float, Dock and Auto Hide.

Figure 15 - Floating, Docking and Auto Hide

Figure 16 - Hidden Views

### **3.2 SCHEMATIC VIEW**

You can add sheets, rearrange the sheet order, and delete schematic sheets.

To add a new schematic sheet, click the plus button to the right of the schematic pane.

Figure 17 – Add Schematic tab

To import schematic sheets, from the File menu, select Import > Schematic. Navigate to the schematic file, select it, and click Open.

To change the order of the tabs, from the Schematic menu, click Order Schematic Tabs and in the dialog box, use the arrows to change the order., and click OK.

To delete a schematic sheet, right-click the sheet tab name and click Yes to confirm the deletion.

### 3.3 SYSTEM VIEW

The System View lists all of the RIMs, slots, and channel IDs in order. You can use this view to reference which channel ID goes to which RIM Slot Pin when determining which IO Port number you want to use within your schematic.

| System View 👻 🕈 🗙                                 |

|---------------------------------------------------|

| RIM 1: FUSION 6 SLOT RIM                          |

| RIM 2: ASM, RIM 6 SLOT MA                         |

| Slot 3: 4xUART RS232/RS4                          |

| Pin 1: UART_000                                   |

| Pin 5: UART_001                                   |

| Pin 9: UART_002                                   |

| Pin 13: UART_003                                  |

| Blot 6: 4xUART RS232/RS₄                          |

| -RIM 3:                                           |

| -RIM 4:                                           |

| □ Fusion: ASM, FUSION CM 12                       |

| Blot 1: 16xDin 24V                                |

| Slot 2: 16xDin 24V                                |

| Slot 3: 16xInverted Din                           |

| Slot 4: 16xDout Source                            |

| Slot 5: 16xDout Source                            |

| Slot 6: 16xDout Sink                              |

| Slot 13: 8xDout Opto                              |

| Blot 14: 8xAin 16 bit Oper                        |

| Blot 15: 8xAout 16 bit -10                        |

| Slot 16: 8xThermocouple      Slot 17: 0 D → 1 D ↓ |

| Slot 17: 8xDout Relay                             |

| Slot 18: 4xUART RS232/R                           |

| Pin 1: UART_008                                   |

| - Pin 5: UART_009<br>- Pin 9: UART 010            |

| Pin 13: UART_010                                  |

| -                                                 |

| Figure 18 System View                             |

#### 3.4 INTERLOCKS VIEW

The Interlocks View shows details of the interlocks which have been designed in Interlock Builder.

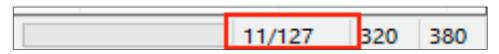

Each interlock you design consists of one or more interlock resources, which is the unit of allocation. In Figure 19 - Interlocks View, the Interlock column shows the individual interlock resources used in a particular design. Each interlock resource has one or more input terms, and those terms are shorn in the Term 1, Term 2, Term 3, and Term 4 columns in Figure 19 - Interlocks View. A Fusion.IO system has a total of 127 available interlock resources. Note that every gate is

converted into AND gates via DeMorgan's law. This means that some gates may take up more interlock terms than others. To learn more, see <u>https://www.electronics-tutorials.ws/boolean/demorgan.html</u>.

The Latch is shown here too where you'll see the name of the latch. To learn more about latches, see section, 4.6 Latches.

Click any logic gate or input port in the schematic drawing to highlight the interlock resources generated by that object in light gray. Click a SOUT port to highlight the interlock resource assigned to the SOUT in yellow.

| Interlocks | View  |          |              |              |              | ▼ д         | × |

|------------|-------|----------|--------------|--------------|--------------|-------------|---|

| Interlock  | Name  | Latch    | Term 1       | Term 2       | Term 3       | Term 4      |   |

| ILK_001    | U0_Y  |          | NOT_DOUT_113 | DOUT_128     | NOT_DOUT_112 |             |   |

| ILK_002    | U2_Y  |          | DOUT_113     | DOUT_130     | NOT_DOUT_112 |             |   |

| ILK_003    | U1_Y  |          | NOT_DOUT_113 | DOUT_129     | DOUT_112     |             |   |

| ILK_004    | U3_Y  |          | DOUT_113     | DOUT_131     | DOUT_112     |             |   |

| ILK_005    | U4_YP |          | NOT_ILK_001  | NOT_ILK_002  | NOT_ILK_003  | NOT_ILK_004 |   |

| ILK_006    | U4_Y  |          | NOT_ILK_005  |              |              |             |   |

| ILK_007    | U5_XA |          | DOUT_160     | NOT_DOUT_162 | NOT_DOUT_161 |             |   |

| ILK_008    | U5_XB |          | NOT_DOUT_160 | DOUT_162     | NOT_DOUT_161 |             |   |

| ILK_009    | U5_XC |          | NOT_DOUT_160 | NOT_DOUT_162 | DOUT_161     |             |   |

| ILK_010    | U5_YP |          | NOT_ILK_007  | NOT_ILK_008  | NOT_ILK_009  |             |   |

| ILK_011    | U5_Y  | DOUT_176 | NOT_ILK_010  |              |              |             |   |

|            |       |          |              |              |              |             |   |

#### Figure 19 - Interlocks View

The Interlocks View is updated whenever any change is made to the schematics drawing, and the total number of used and available interlock resources are shown in the status bar.

Figure 20 - Interlocks Status Bar (used/available)

#### **MONITOR VIEW** 3.5

Digital **Dynamics**

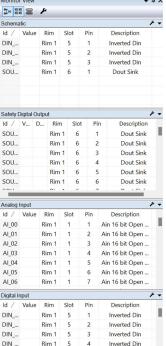

The Monitor View is a dockable pane in Interlock Builder which displays the status of input and output channels present in a connected Fusion. IO system and allows you to filter which channels are displayed according to the channel type and slot card location. You can also view schematic, or field connect information as described Monitor View д x

later in this document. If field connects are imported, the Field Connect view is the default view, otherwise the Schematic view is the default.

Monitor View 🗈 🖩 🗲 Schematic, I/O Monitor, and Field Connect icons

Figure 21 - Monitor View Toolbar Icons

I/O channels are grouped in the Monitor View by general types:

- Safety Digital Output (SOUT) A safety digital output (SOUT) is a digital output channel which can be controlled by a programmed interlock as well as by an EtherCAT master.

- Digital Input (DIN) A digital input channel which can be used as an input term to an interlock.

- Analog Input (AIN) An analog input style channel which can include -10...+10V, 4-20mA, thermocouple, and RTD signals. Analog inputs are not available to be used in Interlocks.

non-inverting digital input, etc.)

Analog Output (AOUT) - An analog output style channel, for example -10..10V and 4-20mA outputs. Analog outputs are not available for use in interlocks.

Detail

Id

Value

RIM Slot Pin

Description

| Monitor panes show the following details for each I/O channel: |  |

|----------------------------------------------------------------|--|

|----------------------------------------------------------------|--|

| Logical ID of the I/O used by Interlock Builder to assign I/O channels to interlocks                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Value of the associated I/O channel</li> <li>1) Digital I/O channels: 1 or 0</li> <li>2) Analog Channels: Physical value (e.g Voltage, Temperature, etc.) or raw<br/>(digital) value</li> </ul> |

| Fusion or RIM device in which this I/O channel is located                                                                                                                                                |

| Slot number in which this I/O channel's slot card is located                                                                                                                                             |

| Slot card pin used by this I/O channel                                                                                                                                                                   |

Specific type of I/O channel (e.g. sourcing or sinking digital output, inverting or

Description

Table 1 - Monitor View Details

Inverted Din

Inverted Din Inverted Din

5

DIN ...

DIN\_...

DIN ...

Rim 1

Rim \*

Rim 1

Figure 22 - Monitor View

Each Monitor pane also has two controls in the upper right corner which can be used to expand or collapse the pane and to set properties such as display filters and format of the channel data.

| Control    |         | Description                                                                                                                         |  |

|------------|---------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| • •        |         | When the arrow is pointed down you can click to collapse<br>the pane. To expand the pane, click the arrow pointing to<br>the right. |  |

| Properties | <b></b> | Opens a properties dialog, which is specific to each<br>Monitor pane.                                                               |  |

Set Display filters using the Monitor properties to control which I/O channels are shown in Monitor view based on:

- Fusion or RIM device where the I/O channel is located

- Slot card on which the channel is located

- Specific type of I/O channel

You can reduce the number of IO channels that are displayed, by removing selected values, which is useful when your system has many IO channels. Select OK to apply the filter.

Use the Analog Input and Analog Output Monitor panes to set whether the channel data value is displayed as a physical (e.g. voltage) or as a raw value. The numerical format for raw values can be set to either decimal or hexadecimal value.

Click the Filter tab of the Monitor Properties and click the checkbox to hide non-Input /Output for that channel depending on your need.

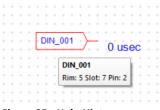

Hover the cursor over an I/P port to view the block's rim, slot, and pin information.

Figure 25 - Help Hint

| Properties                                            |        |                                                 |                      | >      |

|-------------------------------------------------------|--------|-------------------------------------------------|----------------------|--------|

| Filter<br>Signal Filters: Schen<br>Rim Filters: Schen |        | Dim 3                                           | Rim 3                | Dim 4  |

| Available Monitors                                    | Kill 1 | Visible Mo                                      | -                    | Mill 4 |

| Available Promotions                                  | >      | Analog I<br>Digital Ir<br>Safety Di<br>Schemati | iput<br>gital Output |        |

|                                                       | <      |                                                 |                      |        |

|                                                       | <<     |                                                 |                      |        |

Figure 23 - Monitor Display Filters

| Monitor Properties          | ×         |

|-----------------------------|-----------|

| Filter Display Data         |           |

| 🗹 Display raw data          |           |

| Display Type                |           |

| <ul> <li>Decimal</li> </ul> |           |

| OHex                        |           |

|                             |           |

|                             |           |

|                             |           |

|                             |           |

|                             |           |

|                             |           |

|                             |           |

| OK Can                      | cel Apply |

| OK                          | Арріу     |

Figure 24 - Monitor Data Format

### **3.6 SCHEMATIC MONITOR VIEW**

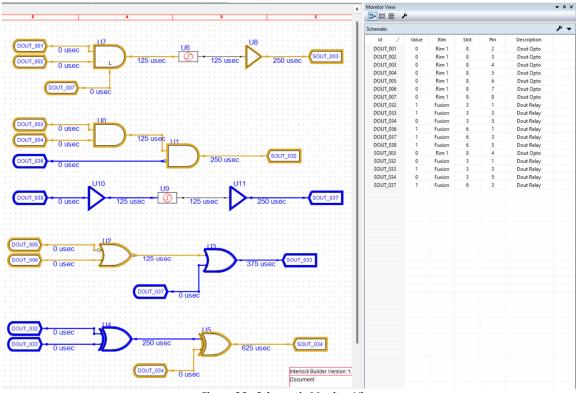

Displays a streamlined representation of the Digital IOs' seen on a schematic sheet. This works the same as the IO Monitor, except that only the IO's in the current schematic tab are shown. Figure 26 - Schematic Monitor View shows a schematic monitor view representing the current schematic IOs.

Figure 26 - Schematic Monitor View

#### 3.6.1 Live Monitor Schematic Indicators

Live monitoring of I/O includes bold highlights around each I/O block, logic gate, and wire in the schematic while the live monitor is being run. A yellow highlight indicates the signal is low and a blue highlight indicates the signal is high.

To enable this mode, connect to the appropriate unit via LAN, open the system project file, and press the live I/O Monitor button within Interlock Builder. This live I/O data updates at a rate of 1Hz.

Figure 27 - Live I/O Monitor Button

IO Port Blocks on the schematic show the appropriate state for the signal given the specifications in the block's Properties View, regardless of the schematic loaded. This data is also mirrored within the Monitor View pane.

Intermediate logic gates and wires, however, are tied specifically to the interlock schematic loaded onto the Fusion.IO device. If the schematic's interlock terms change from what is currently loaded on the Fusion.IO unit, these highlighted signals may be indicative of the actual states of the logical gates. Live first-class timer IO states are not shown on the schematic. Instead, the gate that appears directly before the first-class timer takes the timer's functionality into account

when displaying the live state. For example, if an AND gate fed into a 1 sec ON timer, the AND gate itself is not shown high until it is fed a rising edge and a second has passed to satisfy the timer.

### **3.7 FIELD CONNECT VIEW**

Once you import field connect data, you can view it in Interlock Builder. Field connect data is stored in a CSV file format.

To import field connect data:

- 1. From the File menu, select Import > Field Connect.

- 2. Navigate to where the field connect file is located, select the file, and click Open.

- 3. Click the icons at the top of the Monitor view to change between the Schematic, Monitor, and the Field Connect views.

| Monitor Vie |                |       |             |                     |     | ب ب<br>بر |  |

|-------------|----------------|-------|-------------|---------------------|-----|-----------|--|

| Value /     | Title          | Conne | Signal Name | Туре                | Rim | Slot      |  |

|             | MF2 SLD INTLK  | 15    | CH2A1_FA    | Relay Mo            | 1   | 1         |  |

|             | MF2 SLD INTLK  | 14    | CH2A1_FA    | Relay Mo            | 1   | 1         |  |

|             | MF2 SLD INTLK  | 17    | CH2A2_FA    | Relay Mo            | 1   | 1         |  |

|             | MF2 SLD INTLK  | 16    | CH2A2_FA    | Relay Mo            | 1   | 1         |  |

|             | MF2 SLD INTLK  | 19    | CH2A3_FA    | Relay Mo            | 1   | 1         |  |

|             | MF2 SLD INTLK  | 18    | CH2A3_FA    | Relay Mo            | 1   | 1         |  |

|             | MEA CUR INITUR | 04    | CUDC4 FA    | <b>D</b> 1 <b>M</b> | -   |           |  |

Figure 28 – Field Connect view

Each of the RIMs are listed in the Monitor view window although only one is shown in this figure.

You can view the Connector Pin, Signal Name GND, Type power, RIM, Slot, and Pin details.

### **3.8 PROPERTIES VIEW**

The Properties View shows information about interlock objects (e.g. logic gates, IO Ports, etc.), schematic sheets, and the project document, including several properties which can be customized.

| D    | ocument Number     |                       |

|------|--------------------|-----------------------|

| F    | lev                |                       |

| S    | ize                | A (8.5 x 11)          |

| E    | Hierarchy          |                       |

|      | Sheet 0            | SCH_000               |

|      | Sheet 1            | SCH_001               |

| - E  | Block              |                       |

| 11   | C                  | DIN_000               |

| L    | ocation            | RIM[5] Slot[7] Pin[1] |

| 10   | O Port             | 0                     |

| 10   | О Туре             | DIN                   |

| - Ir | nterlock Resources | 1                     |

| D    | IN Settle Time     | 0.000000              |

| L    | abel               | Input Label           |

|      |                    |                       |

| ab   | ما<br>ما           |                       |

Figure 29 - Properties View

#### 3.8.1 Block Properties

Click any I/O port or logic block to show the properties for that object as shown in Table 2 - Properties of Schematic Blocks.

| Property                     | Purpose                                                                                                               | Editable | Used By                     |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------|-----------------------------|

| ID                           | Logical ID of the block (e.g. U2, DIN_001)                                                                            | no       | All objects                 |

| Location                     | Specifies the RIM, Slot and Pin location of the IO port                                                               | no       | All I/O Ports               |

| IO Port                      | Specifies the physical I/O used by an I/O port                                                                        | yes      | All I/O Ports               |

| Ю Туре                       | Selects if an input port is a DIN or DOUT                                                                             | no       | DIN/DOUT I/O Ports          |

| Interlock<br>Resources       | The number of resources allocated by the object                                                                       | no       | All I/O ports & Blocks      |

| DIN Settle Times             | The amount of time given for the DIN signal to reach a steady state after changing and can be up to 0.063875 seconds. |          | DIN Blocks                  |

| Disable SOUT<br>ECAT Control | Disable or Enable control of an the SOUT port via<br>EtherCAT                                                         | yes      | SOUT I/O Ports              |

| Inputs                       | Sets the number of inputs used by a logic block                                                                       | yes      | Logic Blocks                |

| Enable Latch Term            | Enables and shows the interlock latch pin                                                                             | yes      | Logic Blocks                |

| Timer Function               | Enables embedded timers in logic gates:<br>Type of timer block to use (e.g. ON, OFF, etc.)                            | yes      |                             |

| Timer Period                 | Time interval used by a timer block                                                                                   | Yes      | Intermediate Logic<br>Gates |

| Label                        | Identifies the block.                                                                                                 | Yes      | All I/O Ports               |

Table 2 - Properties of Schematic Blocks

#### SOUT and DOUT

DOUTs are digital outputs that you can use as input terms for interlocks by dragging them from the toolbar. By default, the SOUT and corresponding DOUT are not paired together. Check the "Enable paired ECAT Control" property checkbox to enable the DOUT control. When unchecked, it ignores the ECAT values set via the inherent hidden AND gate.

The paired SOUT and DOUT IO Ports always match. ECAT control can still affect the final SOUT if it is added manually to the schematic via a DOUT IO Port.

#### Notes

You must click the "Disable SOUT ECAT Control" property checkbox if an interlock's SOUT does not require control via EtherCAT.

Changing the number of inputs for a block with signals detaches any signals from the input pins that were removed.

#### 3.9 LOG OUTPUT VIEW

Right-click in the Log Output View and select an option to copy, paste, or clear the log output view.

#### **3.10 SCHEMATIC PROPERTIES**

The title block properties for schematic sheets can be edited in the Properties view, including:

- Main Document Title

- Document Number

- Sheet Title

- Revision

|                 |                                             | Document:<br>System Interlocks   | Title:<br>Machine | e Doors       |            |  |  |

|-----------------|---------------------------------------------|----------------------------------|-------------------|---------------|------------|--|--|

| roperties View  | <b>→</b> ‡ ×                                | Document Number:<br>123-0543-11  |                   |               | Rev:<br>01 |  |  |

| 8≣ 2↓           |                                             | Date: Saturday, April 30, 2022 0 | Sheet: 1 of       | 3             |            |  |  |

| Document        |                                             |                                  |                   |               |            |  |  |

| Title           | C:\Interlock Examples\System Interlocks.ilk | [                                |                   |               |            |  |  |

| Schematic       |                                             | Document:                        | Title:            |               |            |  |  |

| Title           | System Interlocks                           | System Interlocks                |                   | Light Curtain |            |  |  |

| Document Number | 123-0543-11                                 | Document Number:                 |                   |               |            |  |  |

| Rev             | 01                                          | 123-0543-11                      |                   |               |            |  |  |

| Size            | A (8.5 x 11)                                | Date: Saturday, April 30, 2022 0 | Sheet: 2 of       | 3             |            |  |  |

| Hierarchy       |                                             |                                  |                   |               |            |  |  |

| Sheet 0         | Machine Doors                               |                                  |                   |               |            |  |  |

| Sheet 1         | Light Curtain                               | Document:                        | Title:            |               |            |  |  |

| Sheet 2         | Emergency Stop                              | System Interlocks                | Emerge            | ency Stop     | -          |  |  |

|                 |                                             | Document Number:<br>123-0543-11  |                   |               | Rev<br>01  |  |  |

|                 |                                             | Date: Saturday, April 30, 2022 0 | 9:05:01           | Sheet: 3 of   | 3          |  |  |

Figure 30 - Schematic Document Properties

To change the text that displays in the schematic sheet, from the Schematic menu, choose Document Titles. In the dialog box, you can edit the names that display. For example, you can change the Document Number to Document Revision Number.

#### 3.10.1 Adding and Importing Labels

You can add labels as you create I/O ports, or you can import existing field connect signal names to block labels in the schematic. You must have imported a field connect file before you can import the labels.

To add labels to the schematic, select the I/O port you want to label and in the Properties view, scroll down and click Label then type the label you want to use. Note this is only for I/O ports and does not apply to intermediate logic gates (like AND gates).

To import labels, from the Schematic menu, choose Import Labels. Specify the settings you want to use and click Import. You can import labels for all tabs or the current tab, while the Overwrite setting specifies whether existing labels get overwritten.

| Import Labels                                            | ×             |

|----------------------------------------------------------|---------------|

| Filters<br>All Tabs<br>Current Tab                       | Settings      |

| All Tabs Import fieldconnect signals to labels on all so | chematic tabs |

|                                                          | Import Cancel |

Figure 31 - Import Labels Dialog Box

#### 3.10.2 Import label default behavior

You can specify to always import label names statically or dynamically. The static option is the default setting and does not update label names when a new block is added, a block's port number is altered, or a block's type is changed. When you specify dynamic, Interlock Builder automatically updates label names upon addition of a block, or changes in a block's port number or IO type.

From the Schematic menu, choose Properties. Select Static or Dynamic and click Apply.

The Standard Toolbar provides file and edit functions such as:

- Create, Open, & Save schematic documents •

- Cut, Copy, & Paste clipboard selections

- Print schematic document

- Help in Interlock Builder •

### 3.11.2 Schematics Toolbar

The Schematics Toolbar provides quick access to editing tools as well as schematic objects such as IO Ports and Logic Gates.

192.168.9.50

- Edit, Select, Move, Snap to Grid

- **Draw Wire**

- Logic Gates (Buffer, OR, XOR, AND, Armed Latch)

- IO Ports (DIN/DOUT input port and SOUT output port)

- **Design Rules Check (DRC)** •

3.11.3 Program Toolbar

The Program Toolbar provides functions for programming a Fusion or Control Module (CM).

- IP Address: Ethernet IP address of device

- (default is 192.168.9.50) •

- Ping: check the Ethernet connection •

- Program: Program interlocks into device •

#### 3.11.4 Monitor Toolbar

The Monitor Toolbar provides controls to start and stop the monitoring of I/O channels in your system.

Revision: 4.0

- Press the Play button **>** to start the monitoring •

- Press the stop button 🔳 to stop monitoring

Note: You can use the Monitor Properties Field Connect Filter to hide or show certain IO channels depending on your need.

Page 29

Program 🗄 🕨 🔳

Figure 33 - Schematics Toolbar

Ping

Figure 34 - Program Toolbar

Digital Dynamics

**3.11 TOOLBARS**

## **4 DESIGNING INTERLOCKS**

Interlock Builder is a schematic design environment where users can quickly and easily define TÜV certified safety interlocks which are programmed into their Fusion I/O controller. These interlocks can combine digital inputs and outputs distributed among connected Fusion and RIM devices and can include logical objects such as:

- IO Ports

- Logic Gates: AND, OR, XOR, and Buffer

- Timers: ON, OFF, and Pulse

- Latches

### 4.1 INTERLOCK TUTORIAL

Let's create a simple interlock to see how this all works. We will create an interlock and test that it works as designed.

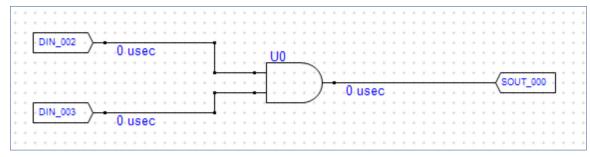

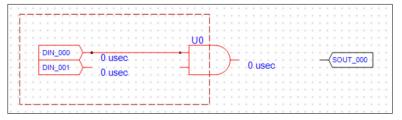

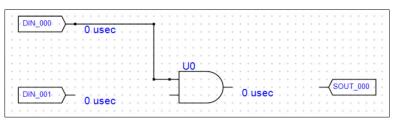

This interlock sets a safe digital output (SOUT) when two digital inputs (DINs) are both TRUE. The following blocks are used in this example:

- (2) DIN Ports

- (1) SOUT Port

- (1) AND Gate

To create an interlock:

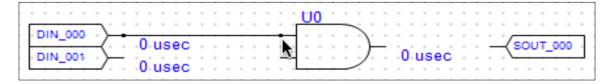

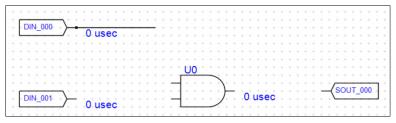

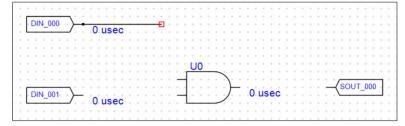

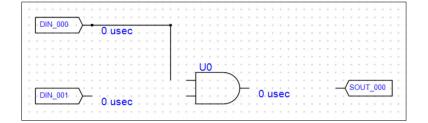

1) Place and arrange the required blocks as shown in Figure 37 -Blocks Placed & Arranged. Sections 5.1-5.3 provide further detail on placing, selecting, and moving blocks.

| + | +             | + | + | +  | +      | +  | + | +   |   | + | +   |    | +        | +  | + | + |   | +   | + | + | +            | + | + | +      |            | +   | + | +              | +             | +      | + | +          |            | +  | +   | ÷  | ÷   | + | + | + |     |      | + | + | +    | + | +   |   | +  | +  | +   | +           | + |    |                   |

|---|---------------|---|---|----|--------|----|---|-----|---|---|-----|----|----------|----|---|---|---|-----|---|---|--------------|---|---|--------|------------|-----|---|----------------|---------------|--------|---|------------|------------|----|-----|----|-----|---|---|---|-----|------|---|---|------|---|-----|---|----|----|-----|-------------|---|----|-------------------|

|   | +             | + | + | ÷  | +      | +  | + | *   | * | + | +   | ÷  | +        | +  | + | * | * | +   | + | ÷ | +            | + | + | +      |            | +   | + | ÷              | +             | +      | + | +          | +          | +  | +   | ÷  | +   | + | ÷ | + | •   |      | ÷ | + | +    | + |     |   | +  | +  | ÷   | +           | + | +  | é : +             |

| + | +             | + |   |    |        | 1  |   | ~   | - | + | +   | ÷  | +        | +  | + | + | + | Ψ., | + | + | +            | + | + | +      | +          | +   | + | +              | +             | +      | + | +          | +          | +  | +   | +  | +   | + | + | + | + - |      | + | + | +    | + | +   | + | +  | +  | +   | +           | + | +  | F                 |

|   | +             | + |   | DI | Ν_     | 00 | 0 | - ) | ⊢ | - | ÷   | ۰. | +        | +  | + | + | + | +   | + | + | +            | + | + |        | +          | +   | + | +              | +             | +      | + |            | +          | +  | +   | +  | +   | + | + | • | ÷   | +    | + | + |      |   |     | + | +  | +  | +   | +           | + | *  | $k \rightarrow 0$ |

| ÷ | +             | + | Ļ | -  | -      | -  | - | _   | + | ÷ | -0  | ÷  | IS       | ec | 2 | + | + | + - |   |   | +            | + | ÷ | +      | +          | +   | Ľ | n              | +             | +      | + | ÷          | +          | +  |     |    | +   | + | + | + | ÷   |      |   |   | -    |   |     | + | +  |    |     | +           | + | +  | F = 0             |

| + | +             | + | + | ÷  |        | +  | + | +   | + | * | ÷   | ÷  | 1        | +  | + | + | + | *   | ÷ | + | +            | + | ÷ | ÷      | ÷          | ° E | Ŷ | <u>v</u>       | -             | -      | ~ | ÷          | +          |    |     | +  | ÷.: | ÷ | + | + | •   |      |   |   | 4    | + | +   | + | +  |    | +   | $\hat{w}$   | + | +  | k = 0             |

| * | +             |   | ÷ | +  |        | +  | + | +   | + | + | +   | +  | +        | +  | + | + | + | *   | + | + | *            | + | + | +      | -          | -   | + | +              |               | +      | - | ۲.         | +          |    | +   | +  | *   | + | + | + | •   |      | + |   | 1    |   |     | + | ~  |    |     | -           | - | ٦. | × +               |

| + | +             | + | + | +  | +      | +  | + | +   | + | + | +   | +  | +        | +  | + | + | + | + 1 | + | + | +            | + | + | +      | +          | -   | + | +              | +             | $^{+}$ | + | ⊢          | -          | ۰. | ÷., | +  | +   | + | + | + | +   | 1    | + | + | +    |   | -   | - | (8 | OL | JT_ | _00         | 0 | 1  | £                 |

| + | +             | + | + |    | +      | +  | + | +   | + | ÷ | ÷   | 1  | +        | +  | + | + | + | +   | + | + | $\pm 1$      | + | ÷ | +      | -          | -   | ÷ | $\overline{z}$ | +             | +      | 2 | 1.         | +          | -1 | J-L | JS | ec  | 2 | + | + | +   | 6.18 |   | + | - +  | + | +   | + | r  | -  | -   | -           | - |    | 1.1               |

| + | +             | + |   |    |        |    | - | ~   | ÷ | + | +   | ÷  | +        | +  | + | + | + | +   | + | + | +            | + | + | +      | +          | - L | ÷ | -              | -             | -      | - | +          | +          | +  | +   | ÷  | +   | + | + | + | •   |      |   | + | +    |   |     | + | +  | +  | ÷   | $^+$        | + | +  | i +               |

| + | +             | + |   | DI | Ν_     | 00 | 1 | + ) | ⊢ | - | ÷., | +  | *        | +  | + | + | + | +   | + | + | +            | + | + | +      | +          |     | + | +              | +             | +      | + | +          | +          | +  | +   | +  | *   | + | + | + | +   |      | + | + | +    |   | +   | + | +  | +  | +   | +           | + | ÷  | $b = 2\pi$        |

| + | +             | + | L | -  | -      | -  | - | _   | + | + | -0  | ÷L | IS       | ec | 2 | + | + | +   | + | + | +            | + | + | +      | ÷          | +   | + | +              | +             | +      | + | +          | +          | +  | +   | +  | +   | + | + | + | +   | +    | + | + | +    | + | . + | + | +  | +  | +   | +           | + | +  | ÷+                |

| ÷ | +             | + | ÷ |    | +      | +  | + | ÷   | + | ÷ | ÷   | ÷  | +        | +  | + | ÷ | + | +   | + | + | +            | + | ÷ | ÷      | +          | +   | + | +              | +             | +      | + | ÷          | +          | +  |     | +  | +   | + | + | ÷ | ÷   |      |   | + |      | + | +   | + | +  |    |     | +           | + | +  | $r \rightarrow 0$ |

| + | +             |   | ÷ | +  | +      | +  | + | +   | + |   | ÷   | ÷  | 4        | +  | + | + | + |     | ÷ | ÷ | +            | + | + | ÷      | +          |     | + | ÷              | $\dot{v}$     | +      | + | ÷          | +          | +  | ÷   | +  | ÷.: | ÷ | ÷ | + | ÷   |      | + |   | - +  | + | +   | + |    | ÷  | ÷   | +           | + | +  | i +               |

| + | $\rightarrow$ | - |   | +  | $\phi$ | +  | + | +   | + | + | ÷   | ÷  | $\phi$ : | +  | ÷ | ÷ | + | +   | + | ÷ | $(\Phi_{i})$ | + | ÷ | $^{+}$ | $^{\circ}$ | 1   |   | +              | $\mathcal{T}$ | $^{+}$ | ÷ | $^{\circ}$ | $^{\circ}$ |    | ÷   | +  |     | ÷ | ÷ | + | 6 D |      | + |   | - 14 |   |     | - |    |    | ÷   | $(\Phi, f)$ | + | +  | 1.14              |

Figure 37 -Blocks Placed & Arranged

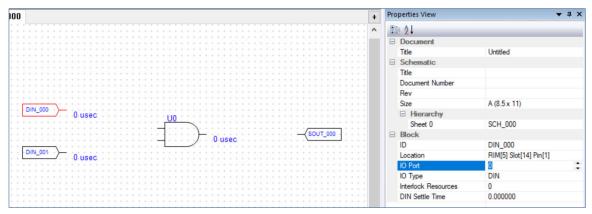

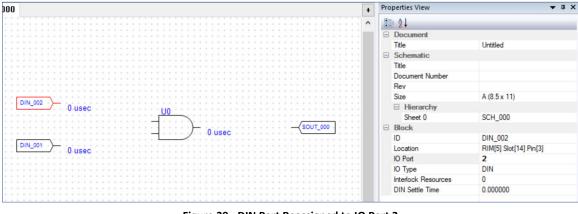

- 2) Change the IO Port properties of each DIN and SOUT port by clicking each IO Port block (Figure 38 Properties of Selected DIN Port ) then changing its IO Port property (Figure 39 - DIN Port Reassigned to IO Port 2). Use the System View to reference which channel ID goes to which RIM Slot Pin when determining which IO Port number you want to use within your schematic. IO Port numbers to use for this example are described here:

- Assign one DIN port to IO Port 2; the name automatically changes to "DIN\_002" after the IO Port property is changed.

- Assign the other DIN port to IO Port 3 and its name automatically is updated to "DIN\_003".

• The SOUT port is assigned to IO port 0; its name becomes "SOUT\_000".

**Note:** Other IO Port values can be used as needed, especially if that is more convenient with your Fusion.IO system hardware.

Figure 38 - Properties of Selected DIN Port

Figure 39 - DIN Port Reassigned to IO Port 2

- 3) For initial testing disable the "Enable Paired ECAT Control" property of the SOUT port.

- **Note**: Leave this property disabled if the final application requires control of this SOUT via EtherCAT. Be sure to re-program the interlocks into the Fusion device after this property is changed.

| ö | 2↓                         |                                    |

|---|----------------------------|------------------------------------|

|   | Document                   |                                    |

|   | Filename                   | C:\Users\Lynn\Documents\Digital Dy |

|   | Schematic                  |                                    |

|   | Title                      |                                    |

|   | Document Number            |                                    |

|   | Rev                        |                                    |

|   | Size                       | A (8.5 x 11)                       |

|   | Hierarchy                  |                                    |

|   | Sheet 0                    | SCH_000                            |

|   | Sheet 1                    | SCH_001                            |

|   | Block                      |                                    |

|   | ID                         | SOUT_000                           |

|   | Location                   | RIM[1] Slot[6] Pin[1]              |

|   | IO Port                    | 0                                  |

|   | Enable paired ECAT Control |                                    |

|   | Assigned ILK               | U0_Y                               |

|   | Interlock Resources        | 1                                  |

Figure 40 – Enable Paired ECAT Control Property

4) Connect blocks with wires. The section 5.4 Inverting PinsInverting Pins, provides details on how to wire blocks to-

Figure 41 - Blocks Connected with Wires

gether.

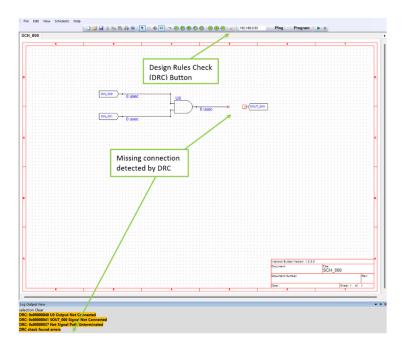

- 5) Click the Design Rules Check (DRC) button to check the schematic for errors, such as missing or incomplete connections.

- An example of how the DRC indicates a missing connection is shown in Figure 42 DRC Detects Missing Connection on SOUT Port

Figure 42 - DRC Detects Missing Connection on SOUT Port

- Figure 43 DCR Completed Successfully shows a Design Rules Check (DRC) for this example which passed successfully.

- Program Fusion.IO system with interlocks. The chapter PROGRAMMING INTERLOCKS provides details on how to

program interlocks into a Fusion device.

| File Edit View Schematic Help         |                                        |                            |             |

|---------------------------------------|----------------------------------------|----------------------------|-------------|

| i 🗋 💕 🛃 🐰 🖦 🛝 🥹 i 📐 i                 | •+# ~00 000                            | V : 192.168.9.50 Ping Pr   | ogram 🗄 🕨 🔳 |

| SCH_000                               |                                        | V DRC (Alt+D)              | +           |

|                                       |                                        | Check Schematic For Errors |             |

|                                       |                                        |                            |             |

| De                                    | esign Rules Check                      |                            |             |

|                                       |                                        |                            |             |

| · · · · · · · · · · · · · · · · · · · | RC) Button                             |                            |             |

|                                       | · · · · · · · · · · · · · · · · · · ·  |                            |             |

|                                       |                                        |                            |             |

| DIN 000                               | ······································ |                            |             |

| 0 usec                                |                                        |                            |             |

|                                       |                                        |                            |             |

|                                       |                                        |                            |             |

|                                       | 125 usec                               |                            |             |

|                                       |                                        |                            |             |

| DIN_001 0 usec                        |                                        |                            |             |

|                                       |                                        |                            |             |

|                                       |                                        |                            |             |

|                                       |                                        |                            |             |

| DRC passed successf                   | fully!                                 |                            |             |

|                                       |                                        |                            |             |

|                                       |                                        |                            |             |

|                                       |                                        |                            |             |

|                                       |                                        |                            |             |

|                                       |                                        |                            |             |

| Log Output View                       |                                        |                            | * a x       |

| selection Clear                       |                                        |                            |             |

| DRC check passed                      |                                        |                            |             |

|                                       |                                        |                            |             |

Figure 43 - DCR Completed Successfully

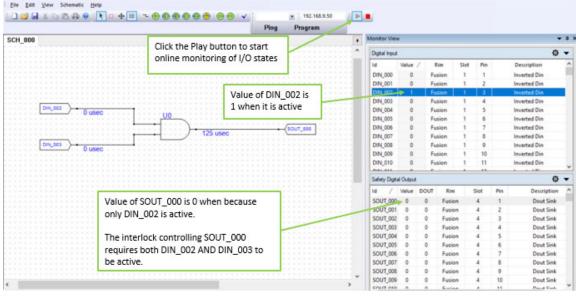

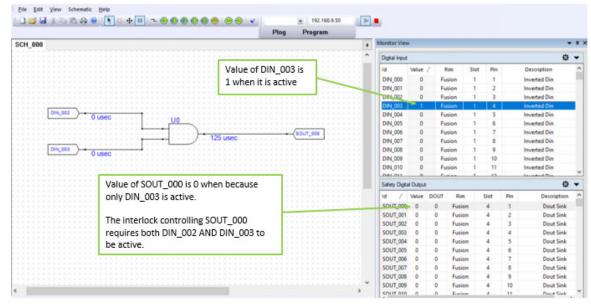

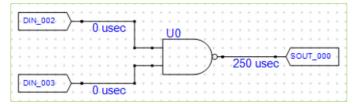

Test the interlock by changing DIN and DOUT states and monitor the results through Monitor View. *Note: further details about Monitor View can be found in the section* Monitor View.

- a) Test DIN\_002 (See Figure 44 Testing DIN\_002).

- i) Click the Play button to start online monitoring of the system's I/O states.

- ii) Activate DIN\_002 and verify in Monitor View that it is active (TRUE). A value of 1 in Monitor View means that the input is active.

- iii) Notice that SOUT\_000 has a value of 0, which means that it is not active (TRUE). This is because SOUT\_000 is controlled by an interlock which is TRUE only when both DIN\_002 and DIN\_003 are TRUE.

Figure 44 - Testing DIN\_002

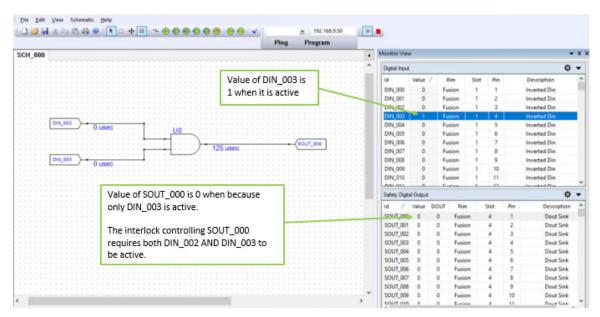

- b) Test with only DIN\_003 (See Figure 45 Testing DIN\_003.)

- i) Activate DIN\_003 and verify in Monitor View that it is TRUE.

- ii) Notice that SOUT\_000 has a value of 0, which means that it is not TRUE. This is because SOUT\_000 is controlled by an interlock which is TRUE only when both DIN\_002 and DIN\_003 are TRUE.

Figure 45 - Testing DIN\_003

- c) Test with both DIN\_002 and DIN\_003 (See Figure 46 Testing DIN\_003.)

- i) Activate both DIN\_002 and DIN\_003 and verify with Monitor View that they are both active (TRUE).

- ii) When both DIN\_002 and DIN\_003 are TRUE, SOUT\_000 will also be TRUE.

- iii) If SOUT\_000 is TRUE in this test, then your interlock is working.

Figure 46 - Testing DIN\_003

After you've completed the tutorial, we'll take a closer look at more design elements.

#### 4.2 SCHEMATIC BLOCKS

Now, let's look at these schematic blocks and how they are used:

- o IO Ports

- Logic Gates

- o Timers

- o Latches

### 4.3 I/O PORTS

I/O Ports designate the inputs and outputs that are used with an interlock. Each I/O Port has a property, "IO Port" which assigns the port to a physical I/O channel.

DOUT 000

Inputs to interlocks can be either:

Digital inputs (DIN) DIN\_000

- or -

Digital outputs (DOUT) which are set via EtherCAT

The type of input used by an I/O Port, DIN or DOUT, is viewed in the Properties View.

**Outputs** which are set by interlocks are safety digital outputs (SOUT)

| -{    | sc        | וכ | J | Т |             | 0 | 0  | 0 |   |    |         |

|-------|-----------|----|---|---|-------------|---|----|---|---|----|---------|

| cked: | • • • • • |    |   | 3 | :<br>:<br>: |   | JT | • | 9 | 01 | • • • • |

• Looks like this when the Enable paired ECAT Control checkbox is checked:

#### SOUT and DOUT

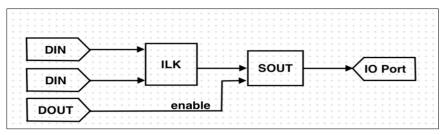

Each SOUT includes a DOUT term which allows the SOUT to be controlled by programmed interlocks as well as via EtherCAT. Effectively the DOUT term acts like an Enable for the SOUT; the actual state of an SOUT's pin is the value of the interlock ANDed with the DOUT value set via EtherCAT.

Figure 47 - SOUT and DOUT

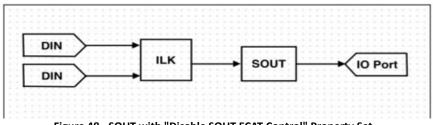

Each SOUT I/O Port has a "Enable Paired ECAT control" property which allows an SOUT to enable inherent paired ECAT Control. When this SOUT ECAT control is enabled, an inherent link is created between that SOUT\_n and the

Figure 48 - SOUT with "Disable SOUT ECAT Control" Property Set

corresponding DOUT\_n. In this case, the DOUT\_n must be asserted, along with the interlock logic being high, for the SOUT channel on the slot-card to be asserted. By default, this property is not set.

When the option for inherent SOUT ECAT control is enabled, the icon for the SOUT IO Port on the schematic updates to visually indicate it is set.

Figure 49 - SOUT with Paired ECAT Control Enabled

When this property is not set, use explicit DOUT gates within the interlock schematic to gain ECAT control.

### 4.3.1 Adding Labels to I/O Ports

You can add labels to inputs and outputs using the Properties view. Select the input or output and in the Properties view, click Label then type a label for that item. See 3.10.1 Adding and Importing Labels.

### 4.4 LOGIC GATES

Interlock Builder provides several logic gates which can be used in interlock schematics.

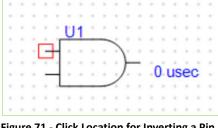

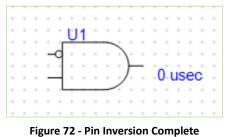

AND, OR, and XOR gates all support up to 32 inputs and provide 2 inputs by default; the number of pins used by a logic gate can be set in the Properties View. Also, input and output pins can be inverted by double-clicking on the pin after the gate is placed in the schematic.

Note: The graphics and truth tables below show the default two input pins for these logic gates.

### 4.4.1 Buffer

The output of a Buffers is:

- TRUE when the input is TRUE

- FALSE when the input is FALSE

A Buffer can be made into a NOT gate by inverting either the input or output.

### 4.4.2 AND Gate

The output of an AND gate is:

- TRUE when all inputs are TRUE

- FALSE in all other cases

#### 4.4.3 OR Gate

The output of an OR gate is:

- TRUE when 1 or more inputs are TRUE

- FALSE when all inputs are FALSE

| Input 1 | Input 2 | Output |

|---------|---------|--------|

| 0       | 0       | 0      |

| 0       | 1       | 1      |

| 1       | 0       | 1      |

| 1       | 1       | 1      |

### 4.4.4 XOR Gate

The output of a XOR (exclusive OR) gate is:

- TRUE when 1 input is TRUE

- FALSE when all inputs are FALSE or multiple inputs are TRUE

| Input 1 | Input 2 | Output |

|---------|---------|--------|

| 0       | 0       | 0      |

| 0       | 1       | 1      |

| 1       | 0       | 1      |

| 1       | 1       | 0      |

| Input | Output |

|-------|--------|

| 0     | 0      |

| 1     | 1      |

Input 2

0

1

0

1

Output

0

0

0

1

Input 1

0

0

1

1

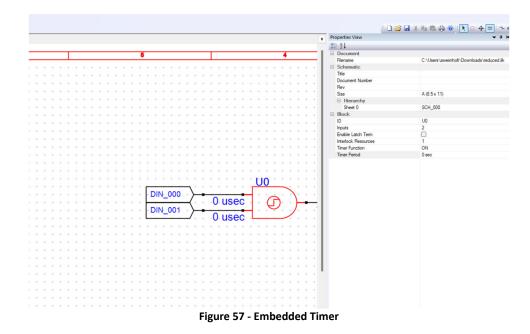

### 4.5 TIMERS

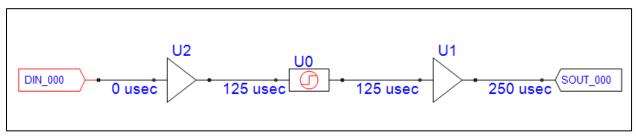

Use timer functions to define timing behaviors within interlocks, for example, adding delays after an input or other interlock signal changes state. Timers can be used with input IO Ports (e.g. DIN or DOUT ports) as well as the outputs of logic gates, other timers, and latches.

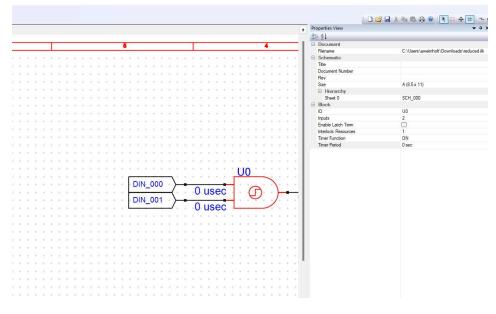

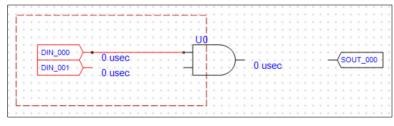

Timers are now embedded in logic gates and timer checking is part of the DRC check. You need to add a logic gate after the timer and the DRC check informs you if it is missing. Legacy projects may need logic gates added before and after the timer depending on how they are constructed.

Figure 50 - Embedded Timer

### 4.5.1 Overview of Timer Functions

The available Timer functions are:

- **ON:** Output set TRUE a fixed time after a rising edge on the input

- OFF: Output set FALSE a fixed time after a falling edge on the input

- PULSE: Output Produces a fixed time duration pulse after a rising edge on the input

- NONE: Disables the timer function; the output

Figure 51 – Timed Interlock Example

A Timer can be embedded into a logic gate through the Properties View. First, select the Timer block in your schematic, then set the Timer Function to a value other than None in the Properties View.

| Pro | perties View       | <b>→</b> ‡ X                |

|-----|--------------------|-----------------------------|

|     | ≣ <mark>≵</mark> ↓ |                             |

|     | Document           |                             |

|     | Title              | C:\Users\rbutler\Desktop\Di |

|     | Schematic          |                             |

|     | Title              |                             |

|     | Document Number    |                             |

|     | Rev                |                             |

|     | Size               | A (8.5 x 11)                |

|     | Hierarchy          |                             |

|     | Sheet 0            | SCH_000                     |

|     | Block              |                             |

|     | ID                 | UO                          |

|     | Timer Function     | ON 🔽                        |

|     | Timer Period       | ON                          |

|     |                    | OFF<br>PULSE<br>NONE        |

Figure 52 - Setting Timer Function

The DRC checks for some sort of logic before and after timers. Logic gates are not needed before embedded timers but are still required after them.

### 4.5.2 Timer Period Properties

The Timer Period for a Timer block is also set through the Properties View. The following units can be used to specify the Timer Period and multiple units can be combined.

- Hours

- Minutes

- Seconds

- Milliseconds (msec)

- Microseconds (usec)

Values for the Timer Period setting can include integer or floating-point values and has a resolution of 125 microseconds. The maximum Timer Period is: 9 hours, 19 minutes, 14 seconds, 431 msec, 875 usec.

#### **Examples:**

- 10 sec

- 5 hrs 20 sec 125 usec

- 1.2 min 0.2 msec

**Properties View →** ¤ × a 2↓ Document Title C:\Users\rbutler\Desktop\Di. Schematic Title Document Number Rev Size A (8.5 x 11) Hierarchy Sheet 0 SCH\_000 Block ID U0 **Timer Function** ON Timer Period 5 sec

Figure 53 - Setting Timer Period

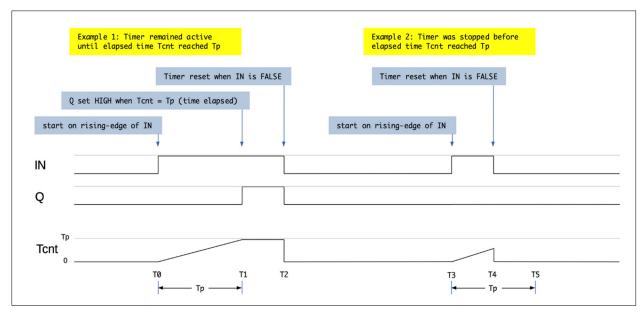

### 4.5.3 Timer ON Details

The Timer ON function sets its output to TRUE a specified time after a rising edge on its input. If a falling edge occurs on the timer's input before the timer period elapses, then the timer's output remains FALSE, and the timer's elapsed time is reset to 0.

Figure 54 - Timer ON Function shows the timer's output (Q) as a function of the input (IN) state, elapsed time (Tcnt), and the user-defined timer period (Tp).

Figure 54 - Timer ON Function

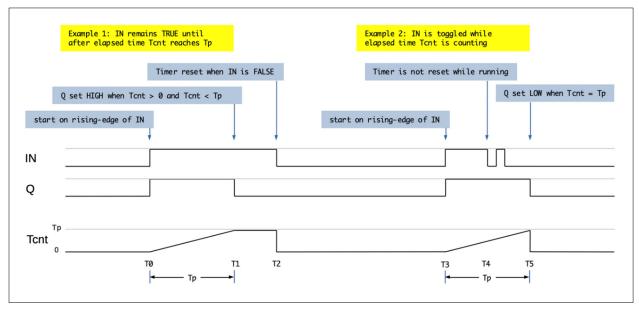

### 4.5.4 Timer OFF Details

The Timer OFF function sets its output to FALSE a specified time after a falling edge on its input. If a rising edge occurs on the timer's input before the timer period elapses, then the timer's output remains TRUE, and the timer's elapsed time is reset to 0.

Figure 55 - Timer OFF Function shows the timer's output (Q) as a function of the input (IN) state, elapsed time (Tcnt), and the user defined timer period (Tp).

Figure 55 - Timer OFF Function

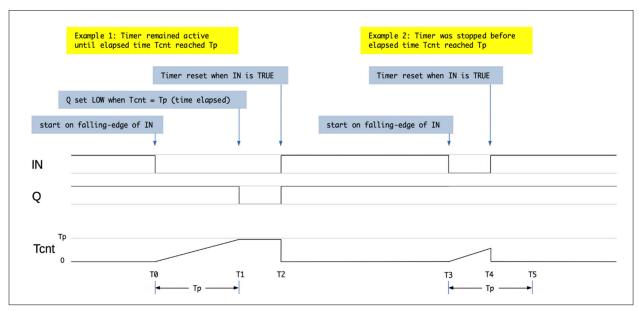

### 4.5.5 Timer PULSE Details

The Timer PULSE function sets its output to TRUE for a specified time period after a rising edge on its input. Even if a falling edge occurs mid-way into the pulse period, the timer's output remains TRUE until the pulse period elapses.

Figure 56 - Timer PULSE Function shows the timer's output (Q) as a function of the input (IN) state, elapsed time (Tcnt), and the user defined timer period (Tp).

Figure 56 - Timer PULSE Function

#### 4.5.6 Embedded Timers

Select Timer Function other than None in the Properties View Window to turn on the timer in a logic gate. Once a Timer Function is selected, the Timer Period becomes enabled so that you can alter the time to your specifications. Once a Timer Function is switched from None, the timer gets drawn inside the logic gate to represent that it now has an embedded timer associated with it.

### 4.6 LATCHES

Interlock Builder provides two types of latching functions which can be used in interlock circuits:

- Hardware (HW) Latch

- Armed Latch

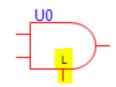

### 4.6.1 Hardware Latch

Hardware latches are part of the standard logic gates (Buffer, AND, OR, and XOR) in Interlock Builder.

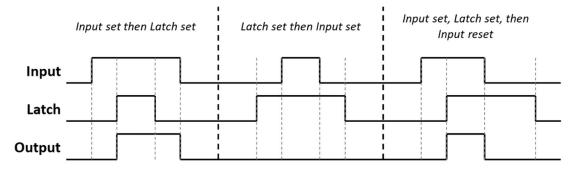

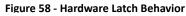

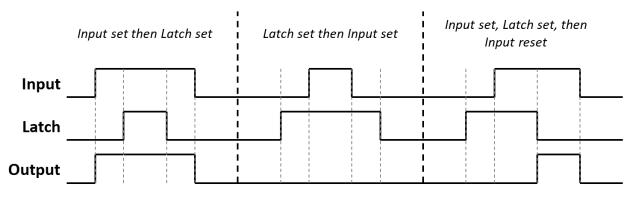

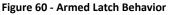

The hardware latch captures the state of the logic gate's input state on the rising edge of the latch:

- Once the input is latched, the logic gate's output stays TRUE until the falling edge of the input

- When the input goes low, the output stays low until the next rising edge of the latch

Figure 58 - Hardware Latch Behavior shows the behavior of a logic gate's output based on the state of the hardware latch and its input(s).

Enable a logic gate's hardware latch from the Properties View by setting the "Enable Latch Term" property. By default, the latch term is disabled.

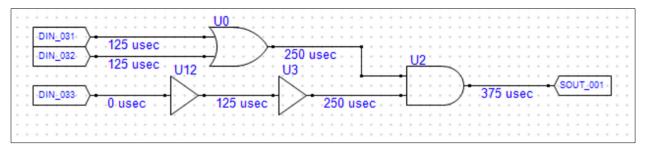

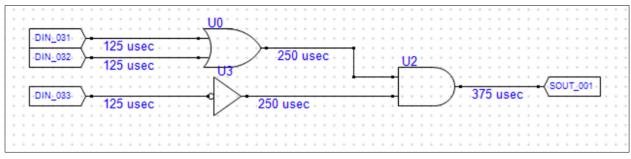

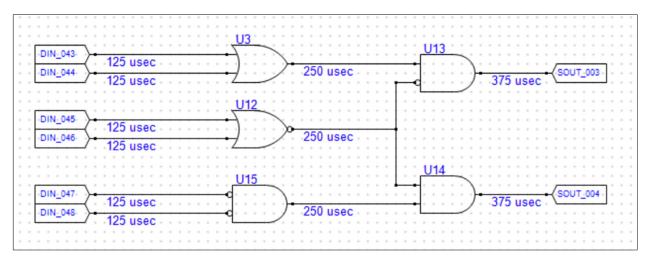

Figure 59 - Enable Latch Term Property shows an example of enabling the latch (highlighted) on a logic gate.